Serial Peripheral Interface

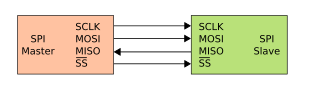

Serial Peripheral Interface (skratka SPI) je synchrónne sériové periférne rozhranie, primárne využívané v rámci vstavaných systémov pre komunikáciu na krátke vzdialenosti medzi riadiacimi mikrokontrolérmi a ostatnými integrovanými obvodmi resp. modulmi (EEPROM, A/D prevodníky, pamäťové karty, displeje, a pod.). Vyvinuté bolo na prelome 70. a 80. rokov 20. storočia spoločnosťou Motorola a v krátkom čase sa stalo de facto štandardom. Obojsmerná full-duplex komunikácia prebieha na spoločnej zbernici, adresácia obvodov je riešená prostredníctvom samostatných vodičov, ktoré zmenou stavu na logickú nulu aktivujú príjem a vysielanie zvoleného zariadenia (vývody SS alebo CS).[1]

Role zariadení na zbernici

[upraviť | upraviť zdroj]- Master

- riadi časovanie prenášaných dát generovaním hodinového signálu

- vyberá, s ktorým zariadením na zbernici bude komunikácia prebiehať pomocou signálu SS – Slave Select (niekedy CS – Chip Select)

- Slave

- prijíma/vysiela podľa hodinového signálu, pokiaľ je aktivovaný pomocou SS/CS

Priebeh komunikácie

[upraviť | upraviť zdroj]- Master nastaví log. 0 na SS zariadenia, s ktorým chce komunikovať.

- Následne začne generovať hodinový signál na SCLK v ktorého takte vyšlú obe zariadenia svoje dáta, pričom MOSI (Master Out, Slave In) vývody zariadení figurujú ako výstup na strane Mastra a vstup na strane Slave a MISO (Master In, Slave Out) naopak ako vstup na strane Mastra a výstup na strane Slave.

- Akonáhle sú dáta odoslané, môže komunikácia buď ďalej pokračovať (Master ďalej dodáva hodinový signál, hodnota SS sa nemení) alebo skončiť (Master prestane generovať hodinový signál a vráti SS na log. 1).

- Dĺžka prenášaných dát je typicky buď 8 bitov (bajt) alebo celočíselný násobok 8 bitov.

Polarita, fáza a frekvencia hodinového signálu

[upraviť | upraviť zdroj]

Vzťah medzi hodinovým signálom a dátami sa určuje dvomi konfiguračnými bitmi, ktoré sa v pôvodnej dokumentácii k SPI označujú ako CPOL a CPHA. Túto konvenciu definuje firma Freescale Semiconductor (pôvodne Motorola) v dokumente „SPI Block Guide“.[2]

- CPOL = 0; pokojová úroveň hodinového signálu je log. 0

- CPOL = 1; pokojová úroveň hodinového signálu je log. 1

- CPHA = 0; vysielajúci mení hodnotu pri zostupnej hrane (predošlého cyklu), prijímajúci číta hodnotu pri nábehovej hrane hodinového signálu

- CPHA = 1; vysielajúci mení hodnotu pri nábehovej hrane, prijímajúci číta hodnotu pri zostupnej hrane hodinového signálu

Niektoré logické analyzátory, vývojové nástroje alebo katalógové listy súčiastok používajú namiesto samostatných CPOL a CPHA príznakov číselný režim (Mode) podľa nasledovnej tabuľky:

| Mode | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

Maximálna frekvencia hodinového signálu, určujúca dátovú priepustnosť zbernice, závisí od limitov komunikujúcich obvodov, zvlášť Slave zariadení (Master môže pre komunikáciu s jednotlivými Slave zariadeniami používať rôzne hodinové takty). Limity sú spravidla uvedené v katalógových listoch obvodov a bývajú v praxi v rádoch jednotiek až desiatok MHz, existujú však aj periférie umožňujúce hodinové takty SPI do 100 MHz.[3]

Referencie

[upraviť | upraviť zdroj]- ↑ Introduction to I²C and SPI protocols [online]. byteparadigm.com, [cit. 2020-11-20]. Dostupné online. Archivované 2020-10-10 z originálu.

- ↑ SPI Block Guide V03.06 [online]. Motorola, 2003, [cit. 2020-11-20]. Dostupné online. Archivované 2015-04-13 z originálu.

- ↑ LTC2376-20 : 20-Bit, 250ksps, Low Power SAR ADC [online]. Analog Devices, [cit. 2020-11-20]. Kapitola ADC timing characteristics, s. 5. Dostupné online.

Pozri aj

[upraviť | upraviť zdroj]- I²C – konkurenčný štandard spoločnosti Philips

Iné projekty

[upraviť | upraviť zdroj] Commons ponúka multimediálne súbory na tému Serial Peripheral Interface

Commons ponúka multimediálne súbory na tému Serial Peripheral Interface

Externé odkazy

[upraviť | upraviť zdroj]- Externí sériové sběrnice SPI a I²C – článok Pavla Tišňovského na serveri Root.cz (2008)

Zdroj

[upraviť | upraviť zdroj]Tento článok je čiastočný alebo úplný preklad článkov Serial Peripheral Interface na českej Wikipédii a Serial Peripheral Interface na anglickej Wikipédii.